- 您现在的位置:买卖IC网 > Sheet目录250 > SFCF2048H1BO2TO-I-M0-523-SMA (Swissbit NA Inc)FLASH SLC UDMA/MDMA/PIO 2G

�� �

�

�

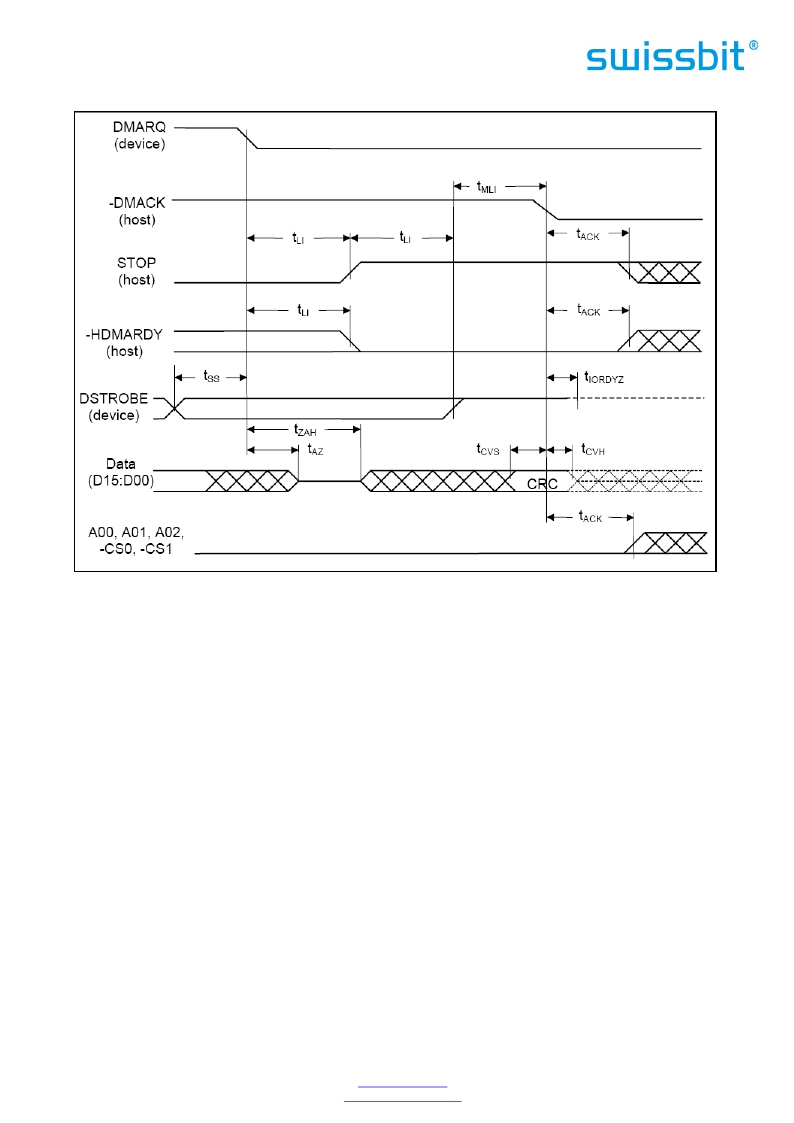

�Figure� 13:� Ultra� DMA� Data-In� Burst� Device� Termination� Timing�

�Notes:� The� definitions� for� the� STOP,� HDMARDY,� and� DSTROBE� signal� lines� are� no� longer� in� effect� after� DMARQ� and�

�DMACK� are� negated.�

�6.5.4.4.5� Host� Terminating� an� Ultra� DMA� Data-In� Burst�

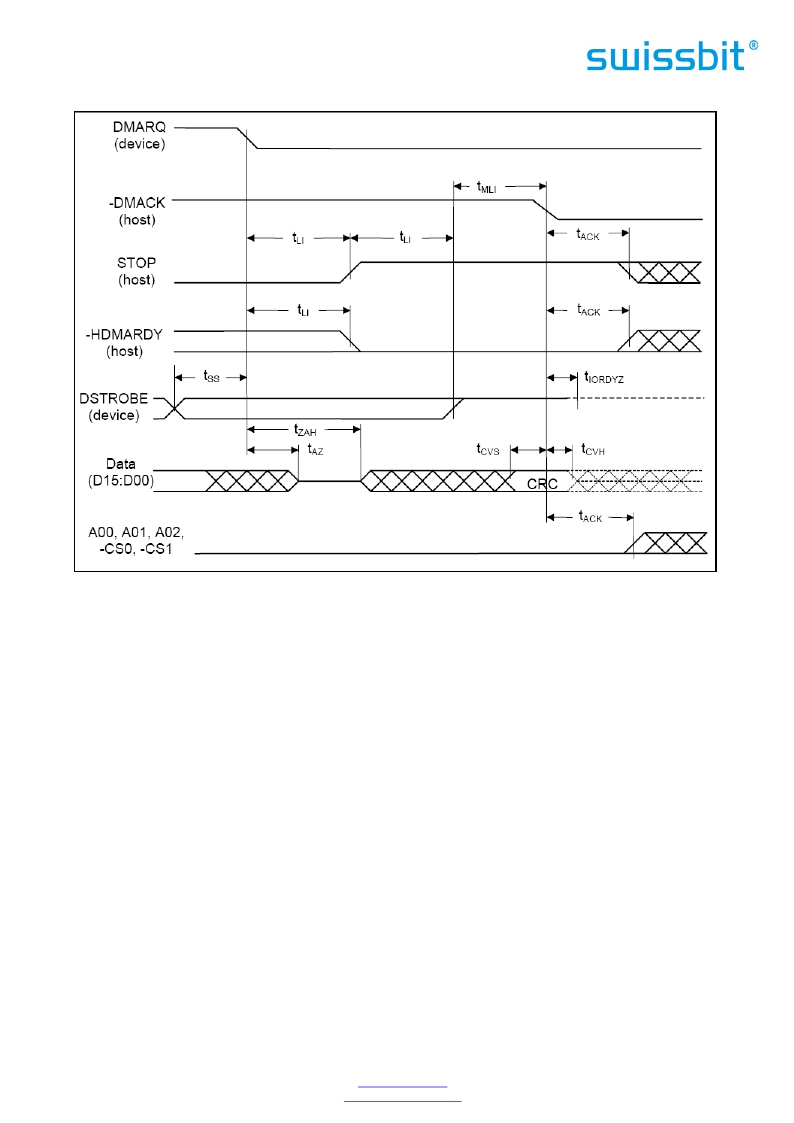

�The� host� terminates� an� Ultra� DMA� Data-In� burst� by� following� the� steps� lettered� below.� The� timing�

�diagram� is� shown� in� Figure� 14:� Ultra� DMA� Data-In� Burst� Host� Termination� Timing.� The� timing�

�parameters� are� specified� in� Table� 27:� Ultra� DMA� Data� Burst� Timing� Requirements� and� are�

��The� following� steps� shall� occur� in� the� order� they� are� listed� unless� otherwise� specifically� allowed:�

�a)� The� host� shall� not� initiate� Ultra� DMA� burst� termination� until� at� least� one� data� word� of� an� Ultra� DMA� burst�

�has� been� transferred.�

�b)� The� host� shall� initiate� Ultra� DMA� burst� termination� by� negating� –� HDMARDY.� The� host� shall� continue� to�

�negate� –� HDMARDY� until� the� Ultra� DMA� burst� is� terminated.�

�c)� The� device� shall� stop� generating� DSTROBE� edges� within� t� RFS� of� the� host� negating� –� HDMARDY�

�d)� If� the� host� negates� –� HDMARDY� within� t� SR� after� the� device� has� generated� a� DSTROBE� edge,� then� the� host�

�shall� be� prepared� to� receive� zero� or� one� additional� data� words.� If� the� host� negates� HDMARDYgreater� than�

�t� SR� after� the� device� has� generated� a� DSTROBE� edge,� then� the� host� shall� be� prepared� to� receive� zero,� one� or�

�two� additional� data� words.� The� additional� data� words� are� a� result� of� cable� round� trip� delay� and� t� RFS�

�timing� for� the� device.�

�e)� The� host� shall� assert� STOP� no� sooner� than� t� RP� after� negating� –� HDMARDY.� The� host� shall� not� negate� STOP�

�again� until� after� the� Ultra� DMA� burst� is� terminated.�

�f)�

�The� device� shall� negate� DMARQ� within� t� LI� after� the� host� has� asserted� STOP.� The� device� shall� not� assert�

�DMARQ� again� until� after� the� Ultra� DMA� burst� is� terminated.�

�g)� If� DSTROBE� is� negated,� the� device� shall� assert� DSTROBE� within� t� LI� after� the� host� has� asserted� STOP.� No� data�

�shall� be� transferred� during� this� assertion.� The� host� shall� ignore� this� transition� on� DSTROBE.� DSTROBE� shall�

�remain� asserted� until� the� Ultra� DMA� burst� is� terminated.�

�h)� The� device� shall� release� D[15:00]� no� later� than� t� AZ� after� negating� DMARQ.�

�i)� The� host� shall� drive� DD� D[15:00]� no� sooner� than� t� ZAH� after� the� device� has� negated� DMARQ.� For� this� step,� the�

�host� may� first� drive� D[15:00]� with� the� result� of� its� CRC� calculation� (see� 6.5.4.5� ).�

�Swissbit� AG�

�Industriestrasse� 4�

�Swissbit� reserves� the� right� to� change� products� or� specifications� without� notice.�

�Revision:� 1.20�

�CH-9552� Bronschhofen�

�Switzerland�

�www.swissbit.com�

�industrial@swissbit.com�

�C-320_data_sheet_CF-HxBO_Rev120.doc�

�Page� 34� of� 101�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SFCF4096H4BK2SA-I-QT-553-SMA

FLASH SLC UDMA/MDMA/PIO 4G

SFCF64GBH2BU4TO-I-NU-517-STD

FLASH SLC UDMA/MDMA/PIO 64GB

SFN08B4702CBQLF7

RES ARRAY 47K OHM 7 RES 8-DFN

SFP1050-12BG

FRONT END AC/DC 1050W 12V

SFP450-12BG

PWR SUP 450W 12V 36.6A W/STANDBY

SFSD1024N1BN1TO-I-DF-151-STD

FLASH MICRO SD CARD IND S-200 1G

SFSD2048L1BN2TO-I-DF-151-STD

FLASH SECURE DGTL CARD SD 2G

SFSD4096L1BN2TO-I-Q2-141-STD

FLASH SECURE DGTL CARD SDHC 4G

相关代理商/技术参数

SFCF2048H1BO2TO-I-M0-533-ZP1

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H1BO2TO-I-M0-543-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H2BU2TO-C-MS-527-STD

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H2BU2TO-I-MS-517-STD

功能描述:FLASH SLC UDMA/MDMA/PIO 2GB RoHS:是 类别:存储卡,模块 >> 存储器,PC 卡 系列:C-440 标准包装:30 系列:- 存储容量:8GB 存储器类型:存储卡 - Extreme III SD?

SFCF2048H2BU2TO-I-MS-527-STD

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H4BK1SA-C-QT-553-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H4BK1SA-I-QT-553-SMA

功能描述:FLASH SLC UDMA/MDMA/PIO 2G RoHS:是 类别:存储卡,模块 >> 存储器,PC 卡 系列:C-300 标准包装:30 系列:- 存储容量:8GB 存储器类型:存储卡 - Extreme III SD?

SFCF2048H4BK2SA-C-DS-553-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH SLC UDMA/MDMA/PIO 2G